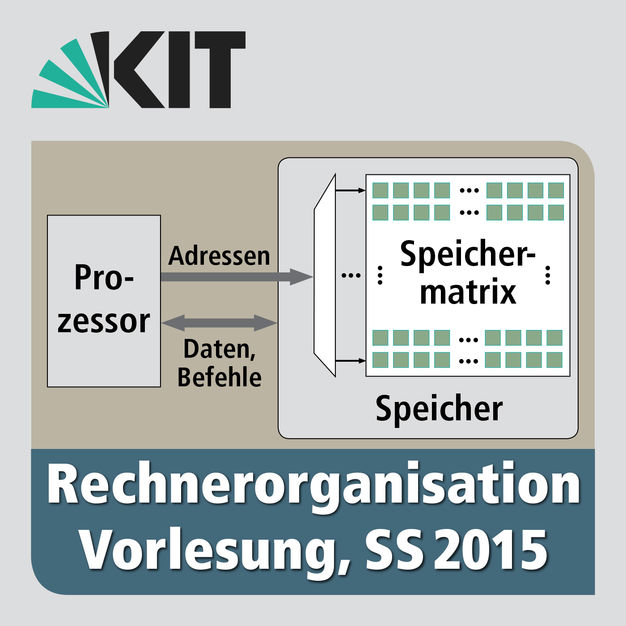

Rechnerorganisation, Vorlesung, SS2015

Der Inhalt der Lehrveranstaltung umfasst die Grundlagen des Aufbaus und der Organisation von Rechnern; die Befehlssatzarchitektur verbunden mit der Diskussion RISC - CISC; Pipelining des Maschinenbefehlszyklus, Pipeline-Hemmnisse und Methoden zur Auflösung von Pipeline-Konflikten; Speicherkomponenten, Speicherorganisation, Cache-Speicher; Ein-/Ausgabe-System und Schnittstellenbausteine; Interrupt-Verarbeitung; Bus-Systeme; Unterstützung von Betriebssystemfunktionen: virtuelle Speicherverwaltung, Schutzfunktionen.

- 1 hour 29 minutesRechnerorganisation, SS 2015, gehalten am 23.04.2015, Vorlesung 0303: Vorlesung | 00:00:07 Kapitel 2: Anforderungen höherer Programmiersprachen: Die Programmiersprache C 00:00:55 Humanoids@KIT 00:08:24 Kapitel 2: Anforderungen höherer Programmiersprachen: Die Programmiersprache C 00:09:01 Vom Quellcode zum ausführbaren Programm 00:11:14 2.3 Grundlagen: Datentypen 00:18:28 Operatoren nach Priorität 00:19:58 2.4 Kontrollstrukturen 00:24:03 2.5 Funktionen und Programmstruktur 00:28:17 Parameterübergabe an Funktionen 00:30:26 Globale und Lokale Variablen 00:31:47 Speicherklassen 00:34:14 2.6 Zeiger und Vektoren 00:41:15 Hierarchie 00:42:28 C-Entwicklerwerkzeuge 00:43:41 Kapitel 3: Zahlendarstellung und Zeichenkodierung im Rechner 00:45:41 Einführung 00:47:24 3.1 Zahlensysteme 00:49:25 Ziffer in Zahlensysteme 00:50:16 3.1 Zahlensysteme 00:54:00 Zahlen-Umwandlung (1) 00:55:00 Euklidischer Algorithmus 00:55:08 3.1 Zahlensysteme Beispiel 00:57:39 Zahlen-Umwandlung (1) 00:57:52 Euklidischer Algorithmus 00:58:56 Beispiel 01:01:48 Beispiel Euklidischer Algorithmus 01:06:02 Zahlenumwandlung (2) 01:07:36 Horner Schema (Beispiel) 01:12:20 Horner Schema (1) 01:12:24 Horner Schema (2) 01:12:37 Horner Schema (3) 01:13:24 Umwandlung des Nachkommateils 01:13:54 Beispiel: Horner Schema 01:17:03 Umwandlung beliebiger Stellenwertsysteme 01:18:21 Beispiel 01:20:47 3.2 Darstellung negativer Zahlen25 November 2015, 5:08 pm

- 1 hour 21 minutesRechnerorganisation, SS 2015, gehalten am 28.04.2015, Vorlesung 04 (Übung 1)04: 1.Übung | 00:00:09 Übersicht für 1. Übung 00:01:19 2.2 Darstellung negativer Zahlen 00:03:59 Darstellung mit Betrag und Vorzeichen 00:10:20 Eierkomponenten-Darstellung 00:18:24 Zweierkomplement-Darstellung 00:37:52 Zahlen in Zweierkomplement 00:38:38 Addition von ZK-Zahlen 00:40:40 Subraktion von ZK-Zahlen 00:41:27 Addition von Zweierkomplement-Zahlen (1) 00:44:04 Addition von Zweierkomplement-Zahlen (2) 00:47:09 Überlauferkennung 00:47:43 Offest-Dual- (Exzess- ) Darstellung 00:48:35 Zusammenfassung der Möglichkeiten 00:50:08 3.3 Fest- und Gleikommazahlen 00:50:53 Festkommazahlen 00:52:25 Gleitkomma-Darstellung 00:53:00 Festkommazahlen 00:55:31 Gleitkomma-Darstellung 00:59:28 Gleitkomma-Maschinenformat 01:01:41 Normierung (IEEE-Standard) 01:02:15 Gleitkomma-Maschinenformat 01:02:55 Normierung (IEEE-Standard) 01:03:21 IEEE-P 754-Floating-Point-Standard 01:04:02 Gleitkomma-Darstellung 01:04:39 Bemerkung 01:06:00 Normalisierung 01:08:19 Zusammenfassung des 32 (64)-Bit-IEEE-Formats 01:11:50 Zusammenfassung des 32-Bit Formats 01:13:58 Aufgabe 1 01:17:36 Aufgabe 2 01:20:44 Rechnerregeln für Gleitkommazahlen25 November 2015, 5:06 pm

- 1 hour 24 minutesRechnerorganisation, SS 2015, gehalten am 30.04.2015, Vorlesung 0505: Vorlesung | 00:00:07 3.2 Darstellung negativer Zahlen 00:01:30 Darstellung mit Betrag und Vorzeichen 00:04:39 Eierkomplement-Darstellung 00:08:55 Zweierkomplement-Darstellung 00:18:19 Beispiel 00:20:31 Offset-Dual- (Exzess- ) Darstellung 00:20:36 Beispiel 00:25:58 Zusammenfassung der Möglichkeiten 00:26:12 3.3 Fest- und Gleitkommazahlen 00:26:27 Festkommazahlen 00:26:50 Gleitkomma-Darstellung 00:29:17 Gleitkomma-Maschinenformat 00:32:50 Normierung (IEEE-Standard) 00:36:21 IEEE-P 754-Floating-Point-Standard 00:38:54 BCD-Kodierung 00:42:44 Zeichenkodierung 00:43:41 ASCII-Kodierung 00:45:25 Platzbeschränkungen 00:51:30 Unicode 00:52:13 Kapitel 4 Befehlssatzarchitektur, Die Hardware-Software-Schnittelle 00:53:12 Architektur (ISA) 01:01:55 Ausführungsmodelle25 November 2015, 5:04 pm

- 1 hour 30 minutesRechnerorganisation, SS 2015, gehalten am 05.05.2015, Vorlesung 0606: Vorlesung | 00:00:08 Ausführungsmodelle 00:19:58 Architektur (ISA) 00:24:28 Datentypen 00:25:53 Datentypen: Gleitkommazahlen 00:27:28 Datentypen 00:32:13 Speicheradressierung 00:48:10 Architektur (ISA) 00:57:43 4.2 Befehlssatz 01:08:49 4.2 Befehlsformate 01:20:34 Befehlsformate des MIPS-Prozessors 01:20:37 Beispiel: Additionsbefehle in MIPS 01:21:45 4.3 Adressierungsarten 01:25:50 4.3.1 Register-Adressierung 01:26:11 Implizite Adressierung25 November 2015, 5:02 pm

- 1 hour 26 minutesRechnerorganisation, SS 2015, gehalten am 07.05.2015, Vorlesung 07 (Übung 2)07: 2.Übung | 00:00:10 Übung 2 | Mikroprogrammierung, MIMA-Architektur, Einführung in die Assembler-Programmierung 00:01:04 Organisationsprinzip des von Neumann Rechners 00:03:23 Zentraleinheit 00:04:32 Zentraleinheit: Leitwerk 00:05:32 Zentraleinheit: Rechnerwerk 00:08:42 Hauptspeicher 00:13:19 Verbindungsstruktur (BUS) 00:16:15 Ein-/Ausgabesystem (Peripheriegeräte) 00:17:15 Komponenten eines von-Neumann Rechners 00:20:29 Aufbau eines einfachen Mikroprozessors 00:29:53 Mikroprogrammierung 00:32:12 Mikroprogramm 00:34:17 Hierarchie 00:35:17 MIMA-Architektur (Mikroprogrammierte Minimalmaschine) 00:35:30 MIMA-Architektur 00:48:22 Befehlsformate, ALU-Operationen, … 01:03:52 Beispiel 01:13:57 Aufgabe 01:16:34 Tri-State-Treiber 01:19:48 Aufgabe 01:21:12 Lösung25 November 2015, 5:00 pm

- 1 hour 28 minutesRechnerorganisation, SS 2015, gehalten am 12.05.2015, Vorlesung 0808: Vorlesung | 00:00:08 4.3 Adressierungsarten 00:06:42 4.3.1 Register-Adressierung 00:07:44 Implizite Adressierung 00:10:03 Flag-Adressierung 00:25:07 Explizite Register-Adressierung 00:26:32 4.3.2 Einstufige Speicher-Adressierung 00:33:23 Unmittelbare Adressierung (imitate Adressen) 00:42:25 Direkte Adressierung (direct addressing) 00:42:31 Absolute Adressierung (extended direct addressing) 00:43:02 Seiten-Adressierung (direct page addressing) 00:52:52 Register-indirekte Adressierung 00:58:50 Indizierte Adressierung (indexed addressing) 00:59:50 Speicher-relative Adressierung 01:04:55 Register-relative Adressierung 01:08:59 Register-relative Adressierung mit Index 01:18:09 Befehlszähler-relative Adressierung25 November 2015, 4:55 pm

- 1 hour 27 minutesRechnerorganisation, SS 2015, gehalten am 19.05.2015, Vorlesung 0909: Vorlesung | 00:00:07 Register-indirekte Adressierung 00:01:35 Indizierte Adressierung (indexed addressing) 00:01:43 Speicher-relative Adressierung 00:05:41 Visualisierung: Register-Adressierung und Einstufige Speicher-Adressierung 00:06:39 Kapitel 5: Ein grundlegendes Rechnermodell 00:08:05 5.1 Organisationsprinzip des von Neumann Rechners 00:14:47 Komponenten des von Neumann Rechners 00:26:28 5.1 Organisationsprinzip des von Neumann Rechners 00:31:27 Komponenten des von Neumann Rechners 00:37:44 5.2 Aufbau eines einfachen Mikroprozessors 00:39:42 5.2.1 Steuerwerk 01:05:16 Phasen der Befehlsausführung 01:08:02 5.2.1 Steuerwerk 01:17:54 Das Steuerregister 01:24:29 Steuerwerk: Fallstudie (1)25 November 2015, 4:53 pm

- 1 hour 29 minutesRechnerorganisation, SS 2015, gehalten am 21.05.2015, Vorlesung 1010: Vorlesung | 00:00:08 5.2 Aufbau eines einfachen Mikroprozessors 00:01:06 5.2.1 Steuerwerk 00:01:21 Phasen der Befehlsausführung 00:10:02 5.2.1 Steuerwerk 00:10:12 Ein-/Ausgabesignale des Steuerwerks 00:11:24 Steuerwerk: Fallstudie (1) 00:11:36 Steuerwerk: Zusammenfassung 00:11:43 Aufbau eines einfachen Mikroprozessors 00:11:55 5.2.2 Rechenwerk 00:19:21 Rechenwerksvarianten 00:22:20 Aufbau eines Rechenwerks 00:23:16 Zeitverhalten des Rechenwerks 00:39:04 Operationen der ALU 00:39:10 Operationsvorrat der ALU 00:39:23 Schiebeoperationen 00:42:38 Rotationsoperationen 00:46:39 Statusregister 00:49:07 Aufbau eines einfachen Mikroprozessors 00:49:16 5.2.3 Registersatz 00:55:39 Daten- und Adressregister 00:55:58 Funktion von Basis- und Indexregister 00:56:39 Automatische Modifikation von Indexregistern 00:57:04 Der (Laufzeit)-Stack »Kellerspeicher« 00:57:07 Automatische Modifikation von Indexregistern 00:58:38 Der (Laufzeit)-Stack »Kellerspeicher« 01:01:53 Hardware-Unterstützung des Stacks 01:02:46 Verwaltung des Stackregisters 01:13:32 5.2.4 Adresswerk 01:14:38 Aufbau eines einfachen Adresswerks 01:16:34 Funktionsweise 01:16:43 Das Adresswerk 01:17:12 5.2.5 Systembus-Schnittstelle 01:19:17 5.2.6 Interne Busse 01:19:23 Weitere Funktionseinheiten 01:20:29 Pentium 4 Prozessor-Architektur 01:22:54 5.3 RISC & RISC 01:24:25 Programmiermodell: Intel 80x86 01:24:28 CISC & RISC 01:24:31 Befehlsaufbau der Intel-x-86-Prozessoren 01:25:15 Mika-Architektur (Übungsblatt 3) 01:25:21 Mikroprogrammsteuerwerke25 November 2015, 4:50 pm

- 1 hour 20 minutesRechnerorganisation, SS 2015, gehalten am 26.05.2015, Vorlesung 11 (Übung 3)11: 3.Übung | 00:00:08 Überblick 00:01:24 Warum MIPS? 00:02:45 Der MARS-Simulator 00:04:55 Installation und Benutzung 00:05:16 Aufbau des MIPS-Prozessors 00:06:33 Registersatz 00:15:43 Speicheraufteilung 00:18:20 Syntax der MIPS-Assemblersprache 00:20:57 MIPS-Assemblerdirektiven 00:25:56 Beispiel: MIPS-Assemblerdirektiven 00:27:49 Systemaufrufe 00:32:59 Beispiel 00:33:32 Ausgabe einer Intergerzahl mit LF 00:35:05 Datenformate im MIPS-Prozessor 00:36:17 Fließkommaformate 00:36:56 Speichermodell 00:38:40 Speichermodell »Big Endian« 00:39:46 Speichermodell »Little Endian« 00:40:07 Speichermodell 00:40:56 Befehlsformate 00:47:15 Adressierungsarten des MIPS-Prozessors 00:49:59 Adressierungsarten in MIPS-Assembler 00:50:16 Befehlssatz 00:55:37 Beispiel: Additionsbefehle in MIPS 00:56:48 Beispiel: Arithmetische Befehle 00:58:33 Struktur eines MIPS-Programms 01:01:51 Beispiel: Integer-Arithmetik 01:02:26 Befehlssatz 01:14:37 Lade- und Speicherbefehle 01:16:15 Beispiel 01:16:53 Unterschied zwischen lb und lbu 01:18:58 Laden von 32-Bit-Operanden 01:19:47 Der globale Zeiger $gp 01:19:54 Befehlssatz 01:20:03 Ersetzung von Pseudoinstruktionen25 November 2015, 4:47 pm

- 1 hour 6 minutesRechnerorganisation, SS 2015, gehalten am 28.05.2015, Vorlesung 12 (Übung 4)12: 4.Übung | 00:00:11 Befehlssatz 00:07:03 Wichtige MIPS-Befehle 00:10:31 Ersetzung von Pseudoinstruktionen 00:13:37 4. Übung: Assemblerprogrammierung mit dem MIPS-Simulator MARS 00:14:05 Programmiertechniken 00:18:13 Stackprogrammierung 00:18:26 Unterprogrammaufrufe 00:28:15 Stack-Rahmen (stack frame) 00:29:12 Beispiel für einen Unterprogrammaufruf 00:31:17 Rekursive Unterprogrammaufrufe 00:36:29 Beispiel 2 00:37:00 Rekursive Unterprogrammaufrufe 00:37:49 Unterprogrammaufruf 00:40:02 Ausnahme- und Unterbrechungsbehandlung 00:45:28 MIPS-Ausnahmen 00:46:04 Beispiele für Ausnahmen 00:50:22 Aufbau des MIPS-Prozessors 00:50:38 Register des Coprozessors 0 00:55:09 Ausnahmebehandlung 00:56:30 Ausnahmebehandlung (Trap Handler) 01:01:08 Abschluss der Ausnahmebehandlung 01:04:04 .set und sbrk25 November 2015, 4:43 pm

- 1 hour 30 minutesRechnerorganisation, SS 2015, gehalten am 02.06.2015, Vorlesung 1313: Vorlesung | 00:00:10 5.3 RISC & CISC 00:05:50 Programmiermodell: Intel 80x86 00:07:55 Befehlsaufbau der Intel-x-86 Prozessoren 00:08:11 CISC & RISC 00:08:54 Mima-Architektur (Übungsblatt 3) 00:09:04 Mikroprogrammsteuerwerke 00:13:12 Implementierung des Steuerwerks 00:13:34 Mikroprogrammierung 00:18:26 CISC (complex instruction set computers) 00:23:16 Limitationen der CISC Architekturen 00:30:48 Prozentualer Anteil von Anweisungen in Hochsprachenprogrammen 00:31:15 RISC (reduced instruction set computers) 00:35:01 Zielvorstellungen für RISC-Rechner 00:35:10 RISC-Rechner aus heutiger Sicht 00:35:15 RISC & CISC 00:35:58 Aufbau eines RISC-Prozessors 00:37:44 RISC - superskalar 00:43:36 Kapitel 6: Pipeline-Verarbeitung 00:44:04 Serielle Befehlsabarbeitung 00:45:58 6.1 Pipeline-Verarbeitung 00:52:50 Pipelining »Fließband-Bearbeitung« 00:53:58 Wäsche-Pipelining 00:54:23 Beispiel 00:57:02 6.1 Pipeline-Verarbeitung 01:05:42 Pipelining 01:06:39 Einfache fünfstellige Befehlspipeline 01:10:26 Definitionen 01:10:37 6.2 Zerlegung in Pipeline-Stufen und Pipeline-Register 01:17:10 Definitionen 01:17:13 Einfache fünfstellige Befehlspipeline 01:19:58 Leistungssteigerung durch Pipelining 01:28:36 Durchsatz25 November 2015, 4:36 pm

- More Episodes? Get the App

Your feedback is valuable to us. Should you encounter any bugs, glitches, lack of functionality or other problems, please email us on [email protected] or join Moon.FM Telegram Group where you can talk directly to the dev team who are happy to answer any queries.